轉載從: Tech News 科技新報

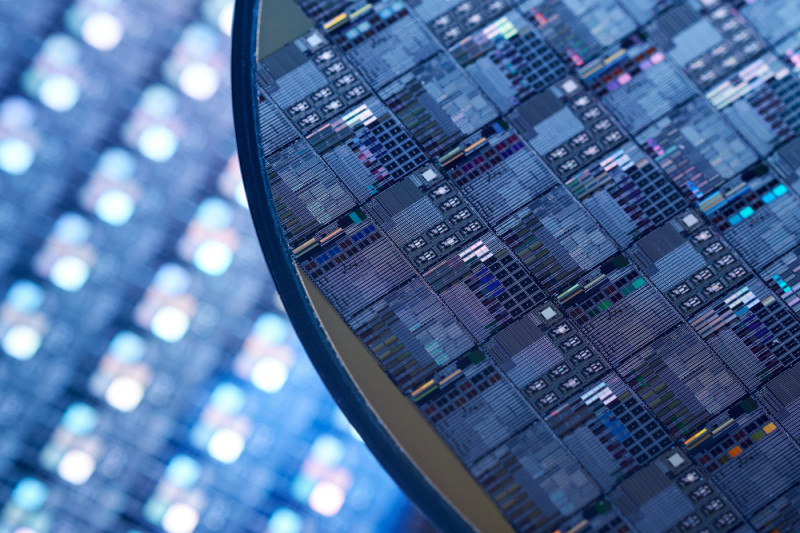

隨著摩爾定律製程微縮的物理極限將至,未來晶片的系統設計與異質整合成為確定趨勢,近 20 年以來 IC 設計的既有思維,已然出現革命性的改變。其中,明導國際(Mentor)所提供的電子設計自動化工具軟體(EDA tool),無疑將成為讓半導體科技充滿無限想像空間的最大助力。

從單純 IC 設計進入系統設計的新時代來臨:參加深度分析

異質整合串聯系統級世代,EDA Tool 成 IC 開發關鍵

IC 設計產業的核心變化,主要驅動力就是高算力、儲存能力提升等「功能的複雜化」,以及追求輕薄短小「產品的極小化」。IC 應用走過單純美好的草創世代,現今邁入多功能穿戴裝置、關顧安全與性能的車用先進駕駛輔助系統(ADAS)、人工智慧(AI)機器人乃至高效能邊緣運算(Edge-computing)等。這是個科幻電影將化為真實的世代,也是一個半導體 IC 設計、晶圓代工(Foundry)、後段封測之間的關係,被「異質整合」(Heterogeneous Integration)概念串聯的系統級世代。

對於 IC 設計產業而言,能有一套完整且簡易操作的 EDA Tool,協助從設計、模擬封裝、驗證、測試等全流程的工具協助,對於 IC 開發流程將是非常重要的關鍵。

透過晶片設計定案(Tape-out)前的完善模擬與測試,降低失效率與預防可能的問題,是現今 IC 設計產業所專注的重要課題。於是在 IC 設計領導廠商聯發科技(MTK)、快閃記憶體控制 IC 設計暨儲存方案龍頭群聯電子(PHISON)等帶動科技無限想像的浪潮中,Mentor 提供的 EDA Tool 成為 design-house 最務實、精準的選擇。

Edge AI 降低雲端負擔,成高算力晶片布局重點

人工智慧概念持續擴散中,從雲端 AI(Cloud AI)全方位連結到邊緣運算 AI(Edge AI),這將使得 AI 晶片於智慧家居、智慧城市、智慧工廠等應用更為廣泛,Edge AI 也將解決延遲問題,扮演 AI 應用普及的關鍵。

以聯發科技近期推出 AIoT 平台 i700 為例,鎖定從語音到影像的訊號處理、識別,必須整合 CPU、GPU、APU、ISP 等等;再加上終端應用百花齊放,聯發科技認為,關鍵在於產品從發想到搶入市場的快、狠、準,時序收斂(closure)勢必需要藉由 EDA Tool 功能提升,再進一步加快晶片從設計到量產的速度,這也將使聯發科技對於 AI 的終極目標「AI everywhere」指日可待。

從雲端到邊緣的高算力 AI 晶片布局從未中斷,聯發科技亦攜手台積電之先進製程、先進晶圓級扇出封裝技術 InFO_OS 量產多晶片異質整合的高效運算(HPC)網通晶片。事實上,全球半導體業者認為以往供應體繫上下游的「接力賽」態勢已然打破,高整合度的 EDA Tool,則將使得半導體從設計、製造、封測,以平台共享資訊方式,一同達到晶片訊號完整性最佳化的目標。

高效運算普及,PCIe 4.0 上下游整合擴大應用

異質整合世代,更包括記憶體、邏輯 IC、RF 元件、類比 IC 等全面納入,對於快閃記憶體控制 IC 先驅群聯電子而言,因為 NAND Flash 儲存應用不斷地擴增,工程師的設計思維已經逐漸轉換,從了解應用環境的需求以及系統面的整合,再進而思考 IC 的功能設計,提升整體系統的效能與使用者經驗。

隨著 AI、5G 趨勢正勾勒出一整個 HPC 系統藍圖,舉凡所衍伸的 8K 生態系、機器學習、邊緣運算等,CPU 大廠紛紛推出支援 PCIe Gen4 的主機板、處理器、顯示晶片等,這意味著,高性能運算應用系統將逐步普及。群聯以 28 奈米製程的 PCIe Gen4x4 NVMe SSD 控制晶片,搭載 96 層堆疊的 3D NAND Flash 儲存方案新品,成為超微(AMD)全球首發合作夥伴,再加上甫於美國 FMS 發佈的首款 DRAM-Less PCIe Gen4x4 SSD 控制晶片等,在在顯示與 AMD、PCIe 4.0 上下游夥伴透過系統面的整合,逐漸擴大應用層面。

而透過完善的 Mentor EDA Tool,可進一步協助設計業者在跨系統或跨平台之間的資料運算轉換更為流暢。而一套完善的 EDA Tool,能在 IC 設計過程中,模擬使用環境以及應用,進行最佳化的調校與驗證,讓工程師們在最短的時間內完成產品上市的目標,進而協助企業將產品轉換成營收、獲利與市佔率,這正是半導體產業競爭力的正向循環。

從單純 IC 設計進入系統設計的新時代來臨:參加深度分析

(首頁:Shutterstock)